|

Contact Information EPM Test Inc. ** Sales ** ** Test Systems Support **

|

| Products > Memory Testers |

|

||||||||||||||||||||||||||||||||||||||||||||||||||

|

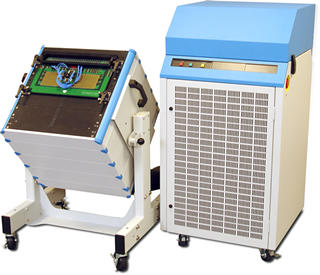

MS5205 General Purpose Memory Test System Maximize Engineering Productivity

The MS5205 test system can be expanded to 144 pin channels suitable for testing a broad range of memory types, from commodity FLASH, SRAM, and DRAM through synchronous devices like SBSRAMs and SDR/DDR SDRAMs. The MS5205 provides functional, AC and DC parametric testing with a scalable test data rate from 104MHz/ 208 Mbps to 208MHz/ 416 Mbps. With VHH individually controlled on every address and clock pin and a parametric test unit (PTU) on each data pin, the MS5205 is an ideal Flash tester. The key to improving engineering productivity is our industry acclaimed TCS software interface- that allows our users to focus on the device under test instead of wrestling with the tester. Tester Control Software (TCS) is based on over 20 years of experience in providing engineers with memory tester software optimized to address the real needs of engineering applications. TCS provides interactive control through an easy to learn and easy to use graphical interface. Test conditions, test flow, multi-parameter analysis tests and more are all instantly changeable. But there are no limits TCS will also seamlessly integrate your user written custom code needed to meet unique testing requirements. Modern memories require specific sequences of commands, addresses and data to be operated or tested. That need is answered with our patented Graphical Sequence Editor (GSE) for creating and editing test sequences. With TCS and GSE combined, there is no more efficient and effective tool for creating, modifying and maintaining complex engineering tests and test programs for semiconductor memories. One of the most powerful tools in identifying and diagnosing weaknesses in a memory device is bitmapping. Our bit-map capture system runs at full tester speed, capturing 1's errors, 0's errors, all errors or a combination of those. With a 32 Gb capacity, the largest memory devices around can be handled with ease. And again, the real key is software. Our bitmap display and analysis software provides rapid navigation, comprehensive analysis and easy export of bit-map data. The MS5205 is CE and SEMI S2 compliant and packaged in a laboratory-sized cabinet with a compact, remote test head (conforming to the industry standard PXI format). The MS5205 remote test head provides the ppin driver and receiver interface to the device under test with 72 Address/clock, 72 Data I/O pins and 32 Logic Control pins, with additional slots for the addition of third party PXI (6U/3U) instrumentation. MS5205 Features:

For more detailed information on the MS5205 test system, contact your EPM Test representative. Contact us

Users can customize the GSE interface to various device architectures and can create a pattern sequence definition in the GSE window using various point-and-click tools to insert, cut, paste and manipulate chip inputs, cycle-by-cycle, until the test pattern sequence has been fully defined. The GSE graphical interface provides easy access to a complete selection of pattern sequence constructs such as:

The GSE understands the concepts behind block programming of various FLASH memories and can also handle the scan testing of block-structured NAND FLASH devices where BAD BLOCKS are defined. All GSE features are aimed at simplifying the task of creating the test pattern sequences for your application. As changes are made to the visual display of the GSE diagram, the system automatically and instantaneously creates the corresponding tester microcode.

The Bitmap Capture Viewer (BCV) provides up to three views of the bitmap data: a navigation view and two additional views that operate independently or as a linked pair. The system collects bitmaps per chip, per test, and per analysis step. The Bitmap Capture Viewer automatically links to the optional Wafermap View Tool. The BCV supports several mappings of the data including topological and electrical layouts. The origin and current cursor position are displayed in the information window in topological and electrical formats. Event counts are available for the full bitmap, by captured plane, by DQ, and by selected row or column. The user can select to display failed bits corresponding to only specific tests, allowing test coverage analysis. EPM Test has included many features in the BCV to enhance engineering productivity. Both bitmap panning and zooming are available, as well as rotate and mirror functions to make the viewed rows and columns match your device orientation. The software also supports a cross-hair cursor coupled with a coordinate address display. There are several mouse and keyboard operations that support cursor motion including: jog to next location, move to next X or Y event, and snap to first X or Y event.

The MS5205 Test System has several hardware-assisted features targeted at specific device types. One such feature for testing FLASH memories is the Parametric Test Unit (PTU) on each data I/O pin. Each PTU can force and sense voltage or current. is that the sense values can be compared and sent to the bitmap system. This is particularly useful for measuring per cell current or voltage threshold distributions.

The hardware provides a third voltage level (0 <= VHH <= 8V) on all address, clock and logic control pins. The system also supports independently programmed levels and timing on all address and clock pins. This function is used to access special test modes within the devices to be tested, particularly Flash memories.

TCS eliminates tedious text and command-driven environments by providing a completely interactive and easy-to-use graphical user interface for system control, program development, test debug, result gathering and archival. Sophisticated software allows you to focus on the device being tested -not the test system. Using simple and intuitive windows operations, users can:

The environment's best feature is the programmer's ability to use as much or as little of the GUI as necessary to tailor the application for the target user. Programmers can also use the GUI in a similar manner to control and parameterize user functions for development of custom user patterns and vector lists.

The test head contains all the pin electronics for 36 Address/Clock pins, 18 or 36 Data I/O pins and 32 Logic Control pins. The pin electronics include a Parametric Test Unit (link to feature) per Data pin and programmable VHH per Address and Logic Control pin. The remote test head accommodates packaged devices and interfaces easily to package handlers, wafer probe stations, Field Ion-Beam, and E-Beam diagnostic systems using an optional Test Head Positioner. |

||||||||||||||||||||||||||||||||||||||||||||||||||